Design & Implementation of Instruction List IL Processor on FPGA Platform Project Abstract:

PLC (Programmable Logic Controller) issued in Industrial process-control applications. PLC contains a CPU core surrounded by memory and I/O peripheral devices. Most of the commercial PLCs available in market uses general purpose processor as PLC CPU. The general purpose CPU is not suitable for PLC in terms of cost and speed. This project proposes an Instruction List (IL) processor compatible with IEC 61131-3 standards. Instruction List isa simple textual programming method for programming of PLC, given by International Electro-Techno Commission As the program of PLC becomes more complex, the execution time taken by the PLC also increases resulting in failure in responding to high speed safety critical logic.

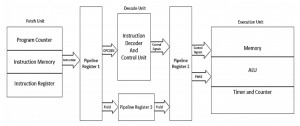

In conventional PLC’s the control specification first converted into instruction set listing that the operating systems can understand. Now a days it is becoming a standard practice to include safety critical function and operation control functions with single ladder diagram programming. Because of this, rungs in the ladder diagram increases and ultimately its performance in terms of speed decreases. For high speed safety critical application the execution time becomes critical. In this project, a 3-stage pipeline is proposed so that each instruction is executed in single processor machine cycle, providing high execution speed required in many high speed safety critical applications.

Problem definition:

Programmable Logic Controllers are widely used in the industrial automation applications. Now-a-days it is a standard practice to include safety critical functions in PLC programming. Also, MEMS based sensors are used in the PLC applications which gives input to the PLC which is very fast changing. The processors used as PLC core are mostly general purpose processors which fail to perform when very high speed of execution is required.

It is desired that processors should be dedicated to PLC tasks, rather than being general purpose and it should employ some technique such as instruction pipelining so as to speed-up the execution of PLC program. Also, the overhead routines should be less in the PLC operations. When this is achieved, PLC can respond to very fast changing inputs. Hence, to achieve fast response from the PLC, it is proposed to design a PLC dedicated Instruction List (IL) processor.